Overview

Most OSs supporting SMP can't meet their performance improvement in spite of hardware advances.

Although the processor technology has been improved conspicuously, most SMP OSs have not following performance improvement as the hardware does. The main reason is that most OSs have a lot of sharing data among threads, which makes them synchronize for each other. More cores take more synchronization traffics, hence the system frequently waste much time to wait for synchronization mechanisms like Lock.

The A2 kernel can give a solution for this.

The A2 kernel is a modern, multi-processor operating system in the tradition of the ETH operating systems Medos, Oberon and Aos. The A2 is composed of light-weight processes that are supported by Active Objects in the language Active Oberon. Active Oberon is a highly readable, abstract programming language with built-in concurrency support. Though the A2kernel is a kind of monolithic kernel, it shares minimal number of data among processes. This feature makes the system faster in the SMP.

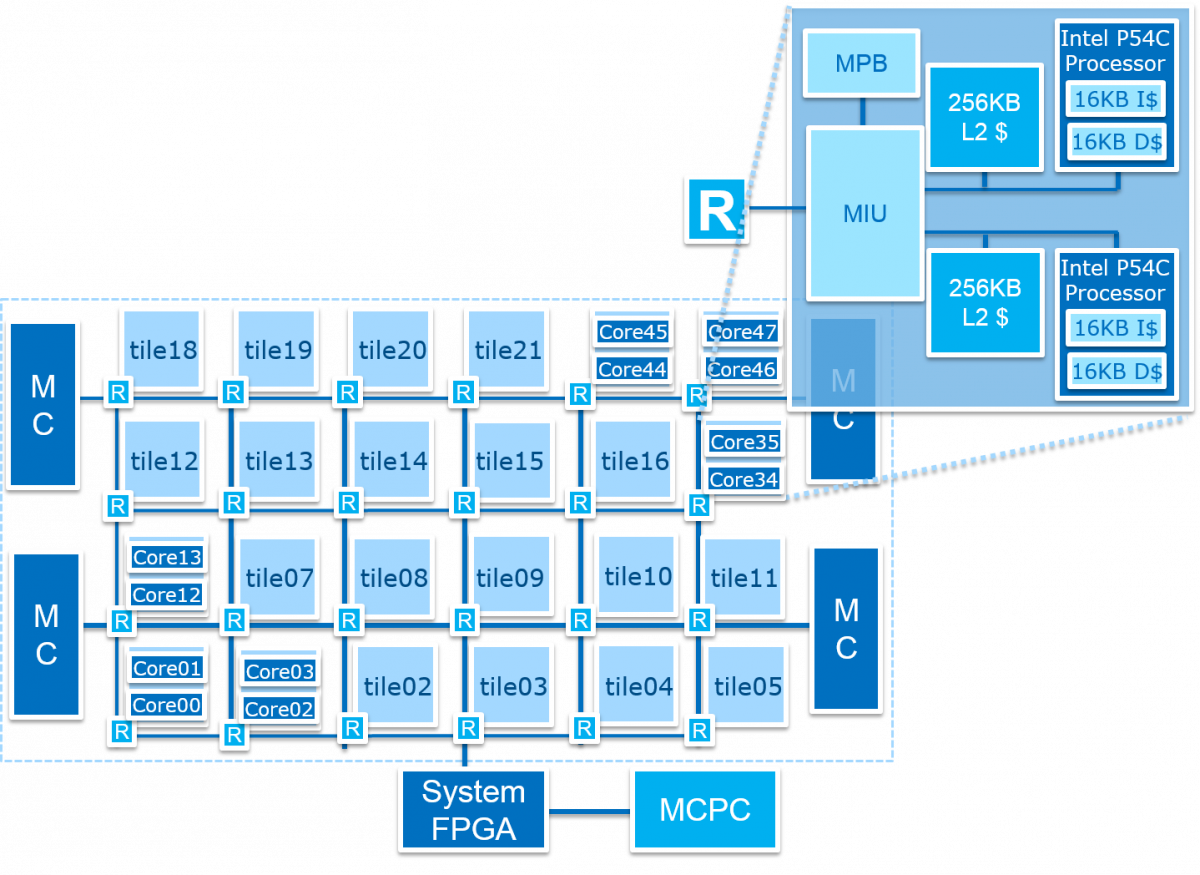

We port the A2 kernel on the SCC which is a experimental many-core platform.

In order to find out more efficient way for OSs to catch up the hardware improvement, we port the A2 kernel on the SCC which is a experimental 48-core chip introduced by Intel. It has no cache coherence among cores, and no hardware support for SMP to perfectly mimic a data center which has multiple independent servers. To port the A2 kernel on the SCC, we had to modify the source from the low-level.

Fig. 1: The SCC and Tile Top-Level Architecture

Contributors

- Suwon Oh, Charles Nguyen, Bernhard Egger

Contact and Bug Report

- Email: suwon@csap.snu.ac.kr